# Digital Power Flexibility & 150-ps PWM Resolution

| UCD7K Family | Fusion Digital Power™ Drivers         | Interface digital controller to power stage; provide protection and bias  |

|--------------|---------------------------------------|---------------------------------------------------------------------------|

| UCD8K Family | Fusion Digital Power™ PWM Controllers | Integrated, digitally controlled, analog PWM and driver to close the loop |

| UCD9K Family | Fusion Digital Power™ Controllers     | Close multiple loops digitally; provide communication and supervision     |

Combining expertise in analog power management and DSP, the revolutionary new family of Fusion Digital Power<sup>TM</sup> products from Texas Instruments provides solutions for a broad range of applications. From AC-line to point-of-load, covering uninterruptible power supplies, server, telecom, data-centric and VRM applications, TI's Fusion Digital Power ICs provide cost-effective solutions with greater levels of performance, reliability and flexibility than today's pure analog designs.

## Available today:

Digital Power Drivers: UCD7100, UCD7201

Digital Power PWM Controllers: UCD8220, UCD8620

Digital Power Controller: UCD9501

High Performance. Analog. Texas Instruments.

For Samples, Reference Designs and Datasheets, visit www.ti.com/digitalpower

Fusion Digital Power, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. M6560 © 2005 TI

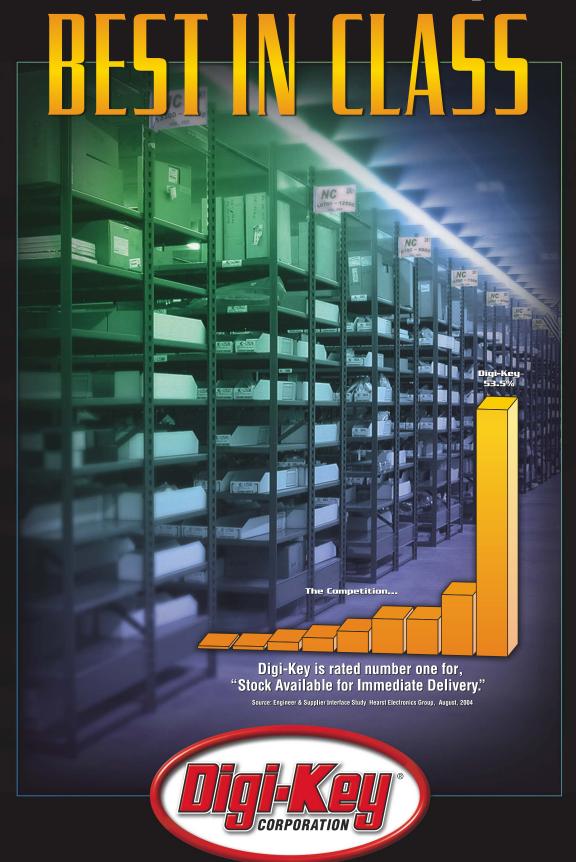

Stock Available for Immediate Delivery

800.344.4539 · www.digikey.com · 218.681.3380

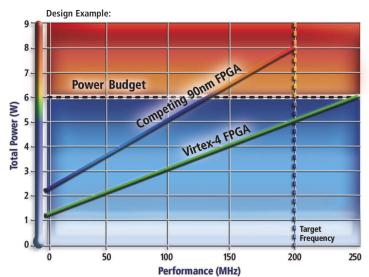

Design Example: LX60 vs. 2S60. Target Frequency = 200 MHz. Worst-case process. 20 K LUTs, 20 K Flip-Flops, 1 Mbit On-Chip RAM, 64 DSP Blocks, 128 2.5 V I/Os Based on Xilinx tool v4.0 and competitor tool v2.1 For higher density devices, achieve up to 5 W lower power

Enter 3 at www.edn.com/info

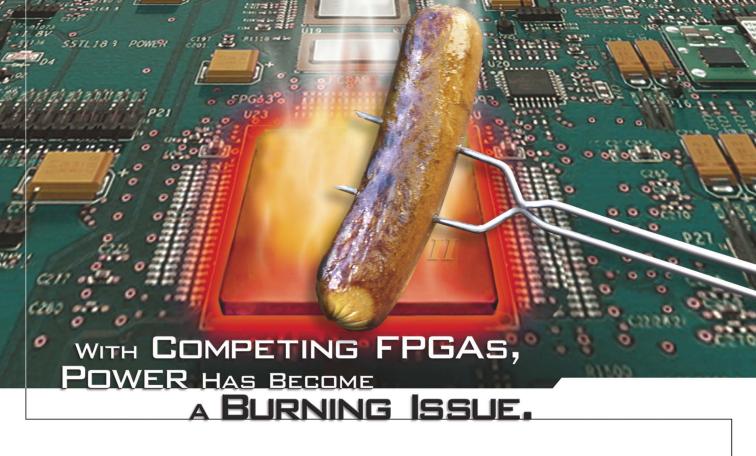

Get 1-5W lower power per FPGA, only with the Virtex-4 family

Check the specs for yourself at realistic operating temperatures  $(T_j = 85^{\circ}C)$ . Different logic architecture or dielectric just won't do it. No competing FPGA comes close to Virtex-4 for total power savings:

- 73% lower static power

- Up to 86% lower dynamic power

- 94% lower inrush current (Take it to the lab and see!)

## UNIQUE TRIPLE-OXIDE TECHNOLOGY & EMBEDDED IP

At the 90nm technology node, power is the next big challenge for system level designers. An inferior device can suffer leakage, dramatic surges in static power, and thermal runaway. That's why we designed our Virtex-4 FPGAs with Triple-Oxide Technology<sup>™</sup>, embedded IP, and power-saving configuration circuitry. Now you can meet your performance goals, while staying within the power budget.

Visit www.xilinx.com/virtex4/lowpower today, and get the right solution on board before your power issues start heating up.

www.xilinx.com/virtex4/lowpower

View The TechOnLine Seminar Today

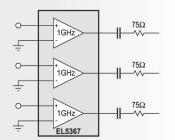

# The first video amp that won't drain batteries or your budget.

#### Performance and value combined ...

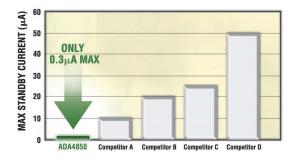

- 0.3 μA max standby current

- Differential gain: 0.12%

- Differential phase: 0.09°

- Rail-to-rail output

- . Supply range: 2.7 V to 5 V

- Single and dual

- 3 mm imes 3 mm LFCSP

- Price: \$0.45 in 100k quantities (ADA4850-1)

## ADA4850: 97% lower standby power, 15% lower priced

Analog Devices' latest video amplifier, the ADA4850,\* provides rail-to-rail output and operates on supply voltage as low as 2.7 V, while offering the industry's lowest standby power. And it does all this and more at a price that's lower than the closest competitor. With its video performance and battery and budget savings benefits, the ADA4850 is the ideal amp to drive all your consumer video designs. To learn more, please visit our website. \*Patent pending

www.analog.com/LowerStandby

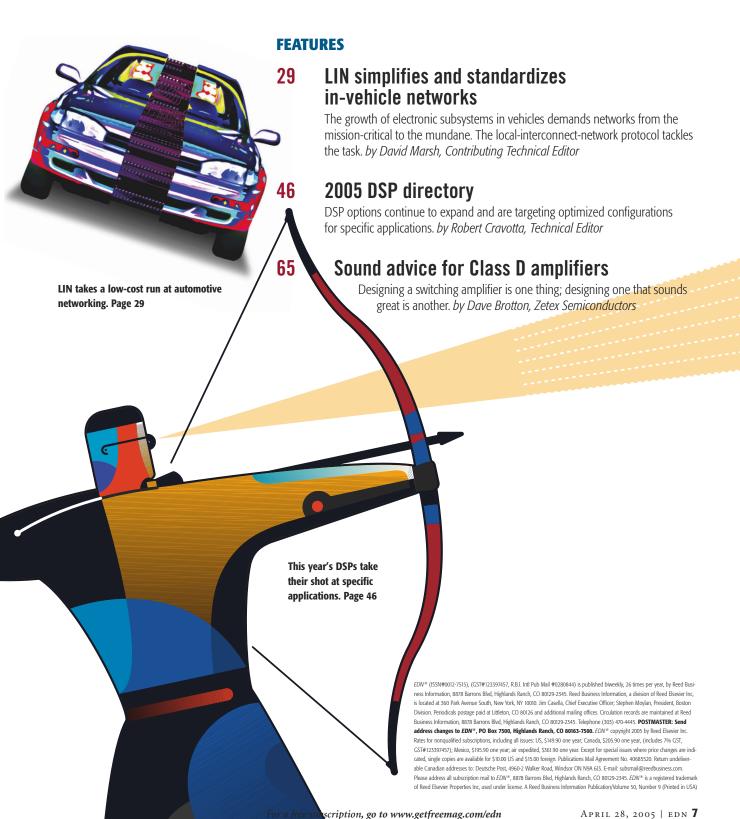

## EDN contents 4.28.05

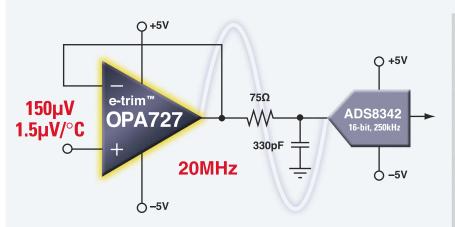

## 150µV max Offset, 20MHz Bandwidth

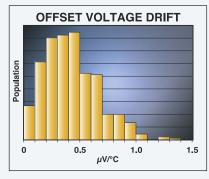

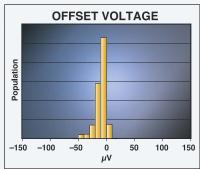

New e-trim™ Technology Offers 1.5μV/°C max Drift

Using the new **e-trim™ technology**, the OPA727 amplifiers are **calibrated** not only for offset voltage, but also for the variation of **offset voltage over temperature** — a **feature offered only by TI**.

| Device    | V <sub>os</sub><br>(μV)<br>(max) | Drift<br>(μV/°C)<br>(max) | Band-<br>width<br>(MHz) | Slew<br>Rate<br>(V/µs) | Supply<br>Voltage<br>(V) | I <sub>Q</sub><br>(mA/ch) | Smallest<br>Package | Price<br>Starts<br>1K |

|-----------|----------------------------------|---------------------------|-------------------------|------------------------|--------------------------|---------------------------|---------------------|-----------------------|

| OPA727/28 | 150                              | 1.5                       | 20                      | 30                     | 4-12                     | 4.3                       | DFN 3x3mm           | \$1.45                |

| OPA725/26 | 3000                             | 4 typ.                    | 20                      | 30                     | 4-12                     | 4.3                       | SOT23               | \$0.90                |

## ▶ e-trim™ Technology

- Post-packaging digital trimming

- Trimming of offset drift for best-in-class temperature stability

- Very tight offset distribution

## **▶** Features

- 150µV max Vos offset

- 1.5V/°C max drift

- Low input current: 10pA

- Wide bandwidth: 20MHz

- Rail-to-rail output

- Wide supply range:4V to 12V, ±2V to ±6V

- Micropackages

MSOP-8 DFN, 3x3mm

#### ▶ Applications

- Precision ADC driver

- Photodiode amplifier

- Active filters

- Medical scanners

- Security scanners

- High-end audio

- Fluid analyzers

**Amplifier Selection Guide** Datasheets and Samples

- www.ti.com/opa727 ○ 800.477.8924, ext. 11999

Dilbert. Page 16

## contents 4.28.05

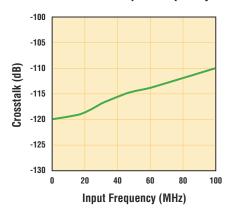

Coplanar connector has low insertion loss and crosstalk. Page 84

#### **LEADING EDGE**

- Programmable servo filters smooth motion control 15

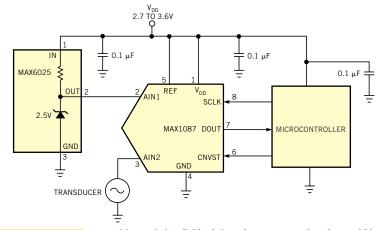

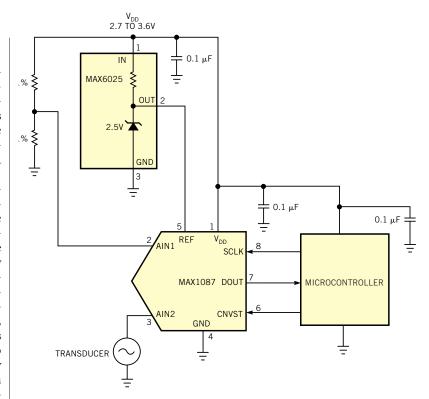

- 15 Resistor array divides, so design conquers ratio needs

- 16 Power-industry coalition announces PMBus standard, forms SIG

- 16 Wi-Fi chip attaches via PCI Express

- 16 Dilbert

- 18 Midpriced, 1.5-GHz-bandwidth DSOs provide an array of features

- 18 VOIP-adapter design boasts \$6 price

- 20 Structured ASIC offers memory-for-logic swapping

- 20 Even jacks are getting smarter

- 22 FPGA development kit targets designs that "race"

- 22 Single-chip FM tuner enables embedded broadcast receiver

## **PRODUCTS**

- 84 Connectors

- 84 Microprocessors

- 86 **Electronic Design Automation**

#### **DESIGN IDEAS**

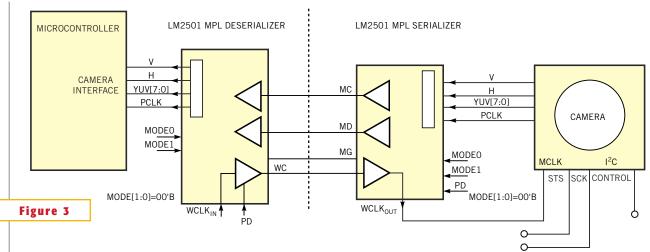

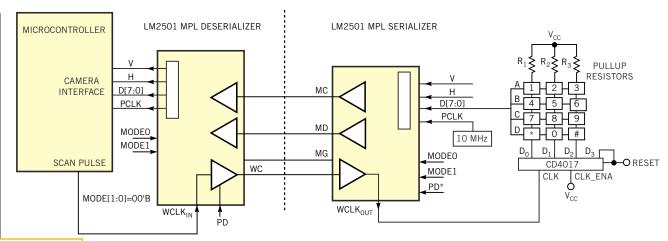

- Camera serializer/deserializer chip set reduces wire count for keypad

- 76 Rearranged reference helps ADC measure its own supply voltage

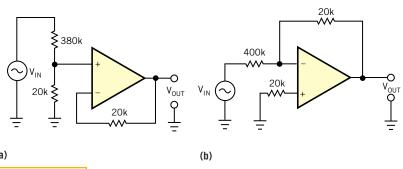

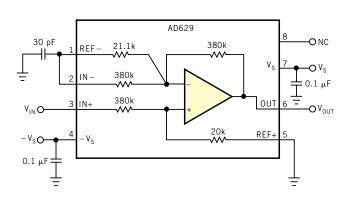

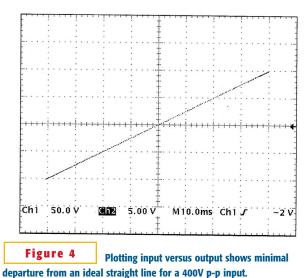

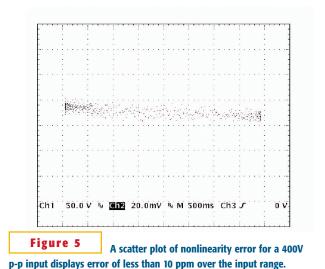

- 78 Difference amplifier measures high voltages

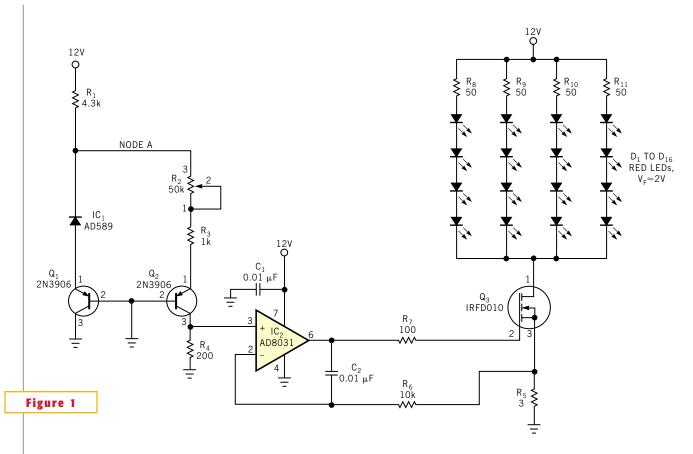

- Linear potentiometer provides nonlinear light-80 intensity control

## **DEPARTMENTS & COLUMNS**

- Crosstalk in differential vias with grounds by Howard Johnson, PhD

- Perception problem dogs engineering 26 by John Dodge, Editor in Chief

- **Editorial Staff** 43

- 44 **Business Staff**

- 86 Advertisers Index

#### The Best of Design Ideas

A selection of your best tricks for tricky problems. www.edn.com/bestofdesignideas

## Submit a Design Idea: Make \$150

www.edn.com/index.asp?layout= siteInfo&doc\_id=30988

#### ONLINE ARTICLES

You think backward compatibility is tough today?

►www.edn.com/article/CA516118

IC design must embrace network effects

►www.edn.com/article/CA516113

Reconfigurable-processing IP targets CE SOCs

►www.edn.com/article/CA516142

Intel releases new NOR for embedded market

►www.edn.com/article/CA515863

Digital Den: Coaxial adapters don't disrupt TV

►www.edn.com/article/CA514859

## **BLOGS**

(Our editors spout off. You spout back.) On The Verge

by Maury Wright, Editor at Large

- Need 1 terabyte for movies and music?

- Video bypasses mobile networks, arrives on handsets

- More

- ►www.edn.com/blog/150000015.html

#### Brian's Brain

by Brian Dipert, Technical Editor

- Open-source bias benefits no one

- Gambling on multimedia

- ►www.edn.com/blog/400000040.html

# 4+32=More Channels. Lots More!

## **Powerful and Simple**

The LeCroy MS-32 mixed signal oscilloscope debugs tough problems in mixed-mode circuits:

- 4 analog and 32 digital channels on one display

- Long memory for outstanding signal capture

- Digital or analog trigger

The LeCroy MSO is the solution you've been waiting for. Available now.

Visit www.lecroy.com for more information.

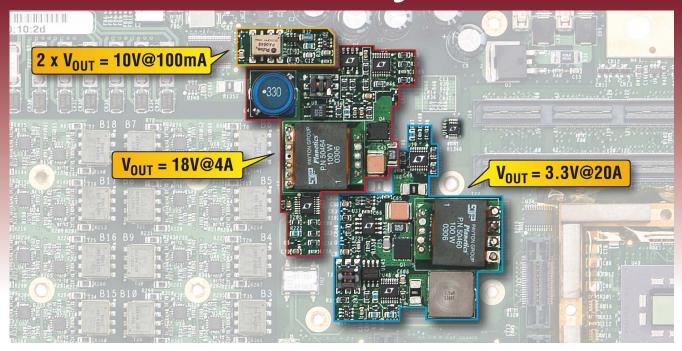

## **Intersil Switching Regulators**

Intersil High Performance Analog

## Running Out Of Room? We Suggest Fewer Chips.

Reduce your board size and increase efficiency with Intersil's multiple output DC/DC Switching Regulators. Get up to 20A of output current and four regulated outputs from a single VIN ranging from 3.3V to 24V.

Design has never been so easy, with a variety of combinations of linears and PWMs, Most devices are available in thin scale packages to maximize real estate.

#### Intersil's Family of Multiple Output DC-DC Solutions

| # of Outputs | Device    | Regulators<br>PWMs | Regulators<br>Linears | Int.<br>FETs | V <sub>IN</sub> (V) | I <sub>OUT</sub><br>(max) (A) | Package         |

|--------------|-----------|--------------------|-----------------------|--------------|---------------------|-------------------------------|-----------------|

| 4            | ISL6521   | 1                  | 3                     |              | 5                   | 20                            | SOIC-16         |

|              | ISL6455   | 1                  | 2                     | <b>√</b>     | 3.3                 | 0.6                           | QFN-24          |

|              | ISL6455A  | 1                  | 2                     | $\checkmark$ | 5                   | 0.6                           | QFN-24          |

| 3            | ISL6537   | 2                  | 2 + Ref               |              | 2.5, 12             | 20                            | QFN-28          |

|              | ISL6532A  | 1                  | 2                     |              | 5, 12               | 20                            | QFN-28          |

|              | ISL6441   | 2                  | 1                     |              | 4.5 to 24           | 6                             | QFN-28          |

|              | ISL6443   | 2                  | 1                     |              | 4.5 to 24           | 10                            | QFN-28          |

|              | ISL6227   | 2                  | 0                     |              | 4.5 to 24           | 16                            | SSOP-28         |

|              | ISL6440   | 2                  | 0                     |              | 4.5 to 24           | 10                            | QSOP-24         |

| 2            | ISL6539   | 2                  | 0                     |              | 5 to 15             | 8                             | SSOP-28         |

| _            | ISL6530/1 | 2                  | Ref                   |              | 5                   | 1                             | SOIC-24, QFN-32 |

|              | ISL6528   | 1                  | 1                     |              | 3.3, 5              | 15                            | SOIC-8          |

|              | ISL6529   | 1                  | 1                     |              | 3.3 to 5, 12        | 15                            | SOIC-14, QFN-16 |

Datasheet, free samples, and more information available at www.intersil.com/edn

Enter 6 at www.edn.com/info

## "It doesn't have to be big to pack a lot of power."

"The MM5 series modular power supply delivers up to 1200 watts in a footprint that's 2/3 the size of the closest competitor. But, unlike the chili pepper, the MM5 remains cool as a cucumber."

Igor Mogilevski, Vice President of Engineering

Our new MM5 series isn't just conveniently sized, it's the highest efficiency, highest-power-density modular power supply on the market. The MM5 series provides

8.7W/cu inch power density with an 80-87% efficiency at full load and offers high output current capacity from a single slot—60A. It can provide up to 900/1200W output in a surprisingly compact package of only 2.5" X 5" X 11" with an isolated 5V@2A stand-by voltage.

That kind of flexibility is what sets Magnetek apart from all the rest. The MM5 Series switch-mode modular power supplies offer fully enclosed power solutions. The common modular assemblies optimize space and the interface signals enhance system intelligence, making these power supplies ideal for the complex power requirements in today's medical, telecommunications, computer and industrial applications.

For further information on the MM5 Series, and a free evaluation unit call **800-621-0733** today or go online at **www.magnetekpower.com/MM5**.

Magnetek Power Electronics Group, 8966 Mason Ave., Chatsworth, CA 91311, 800-621-0733 • www.magnetekpower.com/MM5

## THERE WILL ONLY EVER BE ONE VAN DREBBEL.

**JUST LIKE NOW THERE'S ONLY ONE** D'ESPAIGNET, EVANS, LOUKIANOV, MAASSEL, PATULEA, PETERSON, SCHATTE, AND URSU.

They all started out with the same mission: design something cool using microcontrollers from NEC Electronics. But in the end, only a select few earned the right to have their name mentioned in the same breath as Cornelius Van Drebbel. Here's to the innovations-and the innovators—that would have made Cornelius proud.

## CONGRATULATIONS TO THE WINNERS OF THE NEC ELECTRONICS MICROCONTROLLER DESIGN CONTEST.

HARDWARE CATEGORY ONE [ EV9835 board ]

#### FIRST PLACE

Dmitrii Loukianov Chandler, Arizona LCR Meter

#### SECOND PLACE

**Brian Evans** Vancouver, British Columbia Aquarium Management Unit

## THIRD PLACE

John Peterson Menlo Park, California NEC Tilt Handheld Game HARDWARE CATEGORY TWO [ EV0338 & K0RE9418 boards ]

#### FIRST PLACE

Alain d'Espaignet Jacksonville, Florida **SmartPlanter**

#### SECOND PLACE

Gabriel Patulea Kanata, Ontario Digital Audio Filter

#### THIRD PLACE

**Alvin Schatte** Trenton, Texas Turbine Power Meter E-PAPER CATEGORY

#### FIRST PLACE

Marcel Ursu Burnaby, British Columbia **BrainIRac**

#### SECOND PLACE

Michael Maassel Fargo, North Dakota Car Stereo Tester

What makes a winner a winner? Find out at www.MadDesignContest.com/Winners

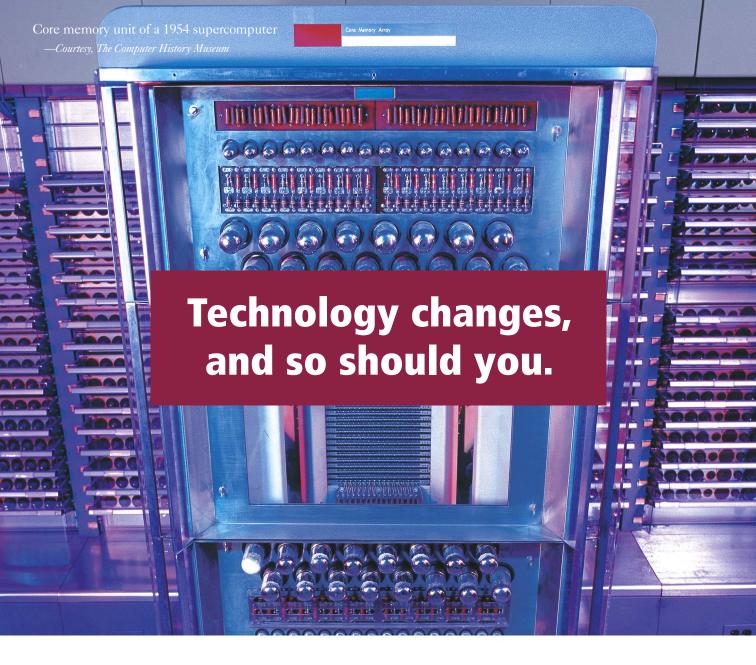

## Introducing *Pro<u>ASIC</u>* Flash FPGAs

ProASIC3 Flash FPGAs aren't just cheaper, they're flat out better.

A new era in low-cost FPGAs is here. ProASIC3 redefines value with true single-chip system design at a price that beats SRAM FPGAs.

**More ASIC, less ASIC alternative.** Gone are the days when you have to choose between nonvolatile or reprogrammable. ProASIC3 has them both.

You can pay more, but you won't get more. That's leadership. Reliability, security, live at power up, low system cost...with so many great features, everything else is history.

Get your free copy of Libero v6.1, our Integrated Design Environment, and see what ProASIC3 can do for you. Visit:

actel.com/pa3

# leading ge

What's hot

in the

design

community

Edited by

Fran Granville

## Image issue

"As long as we continue to view engineering as about widgets and not about people, we will continue to have a perception problem."

-Geoffrey Orsak, Dean, Southern Methodist University, School of Engineering, on the shortage of US engineering graduates

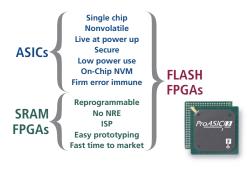

## Programmable servo filters smooth motion control

By Warren Webb

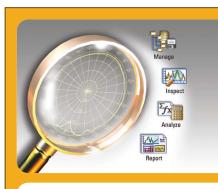

PARGETING MEDICAL, Scientific, and general-automation applications, Performance Motion Devices recently announced the Magellan-PCI motion controller with dual biquad filters. Available in one-, two-, three-, and four-axis versions, the highperformance Magellan-PCI motion-control card supports dc brush, brushless, microstepping, and pulse and direction motors. The dual biquad filters can produce two polarities of lowpass output, as well as highpass, bandpass, and notch filters.

Additional features include trajectory generation, servoloop closure, quadrature-signal input, motor-output signal generation, servo trace, on-the-fly changes, and commutation. The device supplies servo-loop rates as fast as 50

µsec/axis, a 5 million-count/ sec quadrature-encoder-input rate, and pulse and direction output as fast as 5 million pulses/sec. The card accepts input parameters, such as position, velocity, acceleration, deceleration, and jerk, and automatically generates the programmed trajectory. Magellan-PCI prices start at \$638 (OEM quantities).

▶Performance Motion Devices, www.pmdcorp.com.

With dual biquad filters at the output of the servo loop, the new Magellan-PCI motion controller delivers reduced resonance, faster transfers, and smoother motion.

## Resistor array divides, so design conquers ratio needs

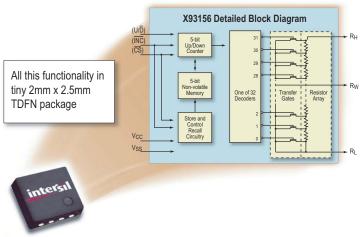

Get precision voltage division using a low-drift, close-tracking ratiometric resistive divider in a two-element SOT-23 or a three-element SOT-143 package.

The venerable resistor divider is still a staple of high-precision analog circuits, because it enables measurement architectures that depend not on absolute component values, but only on their ratios, which are more stable. BI Technologies has put a series-connected, two-resistor divider into a three-lead SOT-23 package, forming a precision voltage divider. The ultrastable resistors of the SSI series are available in standard ratios of 1-to-1, 1-to-4, and 1-to-10. Tolerances are as tight as 0.1%, and the more critical temperature coefficient is ±25 ppm/°C with tracking tolerance better than ±5 ppm/°C.

BI fabricated the resistors using nichrome thin-film technology on a silicon substrate. The device's size lets designers place it close to the circuit area of interest, thus "eliminating the need for the long traces and complex routing schemes required for large networks," according to Mike Torres, application engineer and product marketing manager for BI. The SSI series is also available with three resistors in a network in a four-lead SOT-143 package. Prices begin at 30 cents (10,000).

—by Bill Schweber ►BI Technologies, www.bitechnologies. com.

## Power-industry coalition announces PMBus standard, forms SIG

COALITION OF POWER-SUPPLY and semiconductor companies led by Artesyn Technologies has released Version 1.0 of the PMBus (Power Management Bus) specification, which defines a

protocol to manage power converters and a power system using communication over the SMBus digital-communication bus. The coalition has also announced the formation of an SIG (special interest group), the SM-IF (System Management Interface Forum), to further develop and promote the PMBus power operating system. The SM-IF comprises the PMBus Implementers Forum and the Smart Battery System Implementers Forum. SM-IF will also take over responsibility for the SMBus.

The SMBus is essentially compatible with the I<sup>2</sup>C bus, a popular two-wire bus that handles inter-IC control. "The I<sup>2</sup>C bus is a highly prevalent interface on embedded microprocessors; it's just all over the place," says Michael Stefani, director of product mar-

keting for Artesyn. "SMBus adds an alert line to I<sup>2</sup>C, making it just a short step from I<sup>2</sup>C to SMBus."

In addition to Artesyn, the initial coalition comprises Astec Power and semiconductor manufacturers Intersil, Microchip Technology, Texas Instruments, Volterra Semiconductor, Summit Microelectronics, and Zilker Labs (www.astecpower.com, www.intersil.com, www.microchip.com, www.ti.com, www.vol terra.com, www.summit micro.com, www.zilkerlabs.com).

Conspicuously absent from the SIG is Power-One (www. power-one.com), which last year launched its proprietary Z-One bus and in December announced a design, manufacturing, and marketing agreement with C&D Technologies (cdtechno.com). According to Dave Hage, executive vice president of Power-One, "For complex systems, PMBus does not provide a configuration-controlled, standardized programming interface like the Z-One GUI. Lack of standardization in PMBus converters could make the creation and management of a uniform PMBus GUI virtually impossible."

Hage also points out that a bus architecture is overkill and adds too great an expense for some low-end designs. "For low-complexity systems, customers have requested a configurable point-of-load supply that does not require a bus and is more cost-effective." Power-One developed its "no-bus" Z1000 supplies for these applications.

- —by Margery Conner ►Artesyn Technologies,

- www.artesyn.com.

- System Management Interface Forum, www.power sig.com.

- ► Power Management Bus Implementers Forum, http://pmbus.info/specs. html.

## WI-FI CHIP ATTACH-ES VIA PCI EXPRESS

Broadcom has released what it claims is the first 802.11 wireless-LAN chip that supports the PCI Express bus architecture. The 802.11a/g BCM4311 baseband processor integrates a MAC (media-access controller). The chip's all-CMOS design, high integration, and small footprint provide design flexibility for wireless-enabled notebook PCs, printers, and other client devices, according to Broadcom. "This is a wireless-LAN chip set with our BroadRange technology, which allows devices to hear better in noisier environments with 2- and 5-GHz-band radios," says Brian Bedrosian, Broadcom's senior productline manager for wireless-LAN

The BroadRange DSP technique allows devices to stay connected at distances as much as 50% farther from a wireless router than previous-generation technologies, according to the company. The chip's lead-free package and more efficient footprint make it a good fit for next-generation PC designs.

The device works with the company's OneDriver software, which offers various features, including SecureEasy SetUp software and 125 highspeed mode, to augment the Wi-Fi (wireless-fidelity) network. The software aims to make setup and configuration user-friendly, and the highspeed mode delivers as much as 40% greater throughput than most other 802.11g and 802.11a/g systems. Broadcom's BCM4311, available now in sample quantities, costs \$10 (10,000).

—by Jeff Berman ► **Broadcom**, www.broadcom. com.

## **DILBERT** By Scott Adams

THE PROJECT UNCERTAINTY PRINCIPLE SAYS

THAT IF YOU UNDERSTAND A PROJECT, YOU

WON'T KNOW ITS COST,

AND VICE VERSA.

▶The No. 1 thing consumers search for when they go to the Ask Jeeves search engine is the name of rival search engine "Google," according to Hitwide Inc, a researcher that analyzes the online activities of 10 million US consumers.

16 EDN | APRIL 28, 2005 www.edn.com

## -40° to +85° C Embedded PCs

WinSystems' compact, "go-anywhere" computers and I/O boards can operate where others cannot survive or fit. Rugged, reliable, and built for harsh environments, we provide a PC-compatible architecture that will host standard Linux, Windows, x86 operating systems,

and software development

tools. Our off-theshelf delivery, knowledgeable technical support, and long-term availability makes WinSystems' embedded PCs the right choice for your industrial application.

| Product              | EBC-C3         | EBC-TX  | PPM-TX  | PPM-520 | SAT-SXPlus | PCM-SX |

|----------------------|----------------|---------|---------|---------|------------|--------|

| CPU                  | C3             | Pentium | Pentium | 520     | 386SX      | 386SX  |

| Ethernet             | Dual<br>10/100 | 10/100  | 10/100  | 10/100  | 10/100     | -      |

| Serial               | 4              | 4       | 4       | 4       | 2          | 2      |

| Parallel             | 48 DIO         | 48 DIO  | -       | -       | 24 DIO     | -      |

| LPT, FDC<br>SSD, IDE |                | 1       | 1       | 1       | ✓          | ✓      |

| Size                 | EBX            | EBX     | PC/104+ | PC/104+ | SAT        | PC/104 |

Call 817-274-7553 or Visit www.winsystems.com

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

## Midpriced, 1.5-GHz-bandwidth DSOs provide an array of features

CCORDING TO Boyd Shaw, product manager of Yokogawa Corp of America's Test and Measurement Division, the company's DSOs (digital storage oscilloscopes) are among the best kept secrets in the US electronics industry. Shaw says that YCA's scope sales place it fourth in the United States but that the Japan-headquartered company does far better not only in Asia, but also in Europe. Shaw believes that YCA's US DSO market share will receive a big boost from the introduction of the DL9000 series, which includes four four-channel, 1and 1.5-GHz-bandwidth realtime-sampling scopes, whose prices start at \$10,995.

In the two-channel mode, the 1-GHz units acquire 5G samples/sec on each channel. (With all channels active, the sampling rate drops to 2.5G samples/sec on each channel.) The 1.5-GHz units can sample twice as fast. At each bandwidth, you can choose between units with maximum memory depth of 2.5 or 6.25M samples/channel.

The scopes provide an impressive array of operational and connectivity features, some of which may be unfamiliar to users of US-manufactured DSOs. For example, most US suppliers have now standardized on color grading to indicate the duty ratio of pixel illumination. YCA, however, is sticking with intensity modulation, not, as you might think, because intensity modulation is less expensive or easier to implement than color grading-in a DSO, it is not—but because many users find intensity-modulated displays more intuitive. In this regard, the DL9000s' intensity-graded displays mimic analog-scope displays in a way that many users are bound to find more informative and user-friendly than color-graded displays.

The DL9000 designs go to great lengths to rapidly acquire lots of waveforms with minimal time between acquisitions and to quickly display the acquired data in the most meaningful ways. By segmenting memory when the record length is shorter than the full memory depth, the scopes can acquire waveforms with minimal time between acquisitions. One display mode uses the intensity-grading feature to create a single display that overlays the multiple acquisitions. However, all data from each acquisition remains in memory, and you can individually inspect each waveform to search for anomalies. If the accumulated length of all waveforms exceeds the memory depth, the unit discards the oldest acquisitions from the FIFO memory.

Other features include both front- and rear-panel USB ports, an optional 100Base-TX/10BaseT Ethernet interface, a trigger-comparator output for use with external equipment, a go/no-go output for use in production testing, an optional built-in stripchart recorder, and two PCMCIA slots. (By installing an appropriate card in one of these slots, you can add an IEEE 488 interface.) The units have many built-in filtering and statistical functions. Unlike most Windows-based DSOs, these scopes run under a ROM-resident version of Windows CE. Shaw says that the results are faster start-up, greater operational stability, and more room for your data on the optional 20-Gbyte in-

►Yokogawa Corp of America, 1-770-254-0400, www.yoko gawa.com/us/.

## **VOIP-ADAPTER DESIGN BOASTS \$6 PRICE**

Telecommunications and networking vendor Vocal Technologies has rolled out a line of VOIP (voice-over-Internet Protocol) ATA (analogtelephone-adapter) designs, including a simple ATA with a \$6 BOM (bill-of-materials) cost and a full-motion IP videophone with a \$30 BOM.

The designs employ DSP resources and thereby eliminate the need for an additional RISC processor, according to the company. The adapter design offers a single PSTN (public-switched-telephonenetwork) port and connects to a PC via USB. The design supports two telephone lines, two Ethernet lines, and a PSTN "life-line" port for automated voice-service switching in the event of a power outage or a network disconnection.

John Blume, Vocal's chief executive officer, says that these designs reduce the number of common building blocks and components necessary for developing ATAs. "Our approach to ATA is different from many others, because we eliminate the RISC processor, which, in turn, drives down the BOM for designers," Blume says. When developing its designs, Vocal looked at alternatives using both DSPs and RISC processors and found that a recentgeneration DSP is suitable for running the entire application. "The idea here is to take away most of the mystery for designers and suppliers, so that they have what they need," Blume says. -by Jeff Berman

▶Vocal Technologies, www.

vocal.com.

DL9000 series scopes do a few things that some other DSOs can't do. For example, DL9000s can display Lissajous figures (lower half of the screen).

►According to a recent report from IBM, 76% of all e-mails in February 2005 were spam, down from a summer 2004 peak of nearly 95%.

18 EDN | APRIL 28, 2005 www.edn.com

**FPGA Design** Ever feel tied down because your design tools didn't support the FPGAs you needed? Ever spend a weekend learning yet another new design tool? Maybe it's time you switch to a truly vendor independent FPGA design flow. One that enables you to create the best designs in any FPGA. Mentor's full-featured solution combines design creation, verification, and synthesis into a vendor-neutral, front-to-back FPGA design environment. Only Mentor can offer a comprehensive flow that improves productivity, reduces cost and allows for complete flexibility, enabling you to always choose the right technology for your design. To learn more visit us at **www.mentor.com/techpapers** or call us at **800.547.3000.**

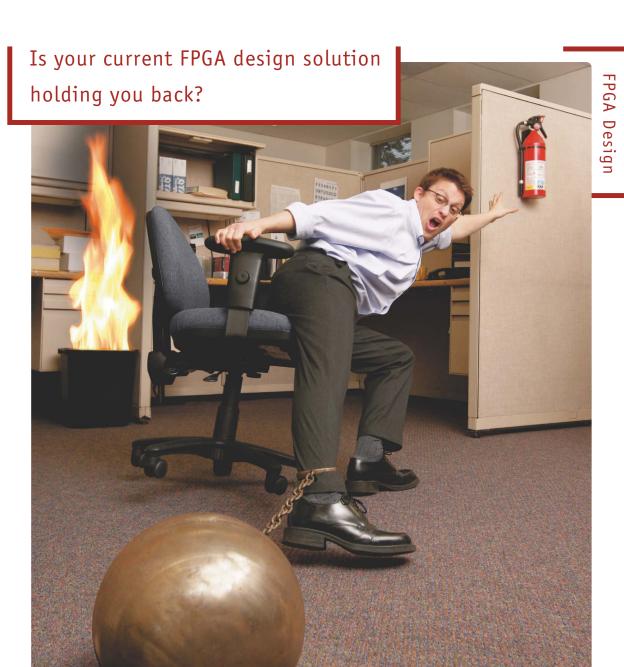

## Structured ASIC offers memory-for-logic swapping

CONFIGURABLE-CORE and structured-ASIC vendor eAS-IC Corp and its partner Flextronics Semiconductor have released a structured ASIC that allows users to configure the amount of logic, memory, and reprogrammable logic they need for a given design. The company's executive vice president for marketing, Ronnie Vasishta, says that the

Implemented on 0.13-micron STMicroelectronics silicon, the FlexASIC architecture boasts as many as 3 million ASIC gates, as much as 1.5 Mbits of SRAM, and operation as fast as 400 MHz.

fabric gives users the best of the FPGA and the ASIC worlds: the density and speed associated with ASICs without the NRE (nonrecurringengineering) costs and the programmability of FPGAs without the power and performance shortcomings. "FlexASIC offers a 25- to 30times density improvement over FPGAs with power density and performance akin to cell-based design," says Vasishta, claiming FlexASIC operates at approximately 400 MHz.

The FlexASIC architecture boasts a field of proprietary SRAM three-input LUT (look-up-table)-based logic cells,

called eCells (embedded cells), surrounded by embedded-SRAM blocks, PLLs, an 8051 microcontroller, and ROM blocks. Configurable I/O surrounds all of these blocks. The FlexASIC architecture allows users to swap eCells for extra SRAM if a design requires. For example, the biggest device in the FlexASIC family, the FA3000, boasts 3 million ASIC gates in the form of 92,000 eCells, or 194,000 LUTs, plus 2.8 million bits of embedded single-port SRAM.

Designers can configure some eCells after fabrication to reprogrammable-logic blocks. The companies program a device's eCells, RAM, and embedded RAM during fabrication using "e-beam" technology,

which customizes the vias between the sixth and seventh layers of the eight-layer process. The routing customization differs from programming the logic and programmable-logic blocks. The companies use a bit stream for this programming and can reload the blocks for debugging after fabrication.

The companies also built a clock tree into the fabric, which means that users need not build it but also that they can't adjust it. The companies offer users two design flows to configure and program the devices. Using the first flow, designers feed a Verilog or VHDL netlist into Synopsys' (www.synopsys.com) Design Compiler, which creates a gate-level netlist. Users then perform chip-resource allocation, assigning memory, clocks, and I/O on the design. Then, using a proprietary eTools suite, users perform mapping, placement, and, with technology from OEM Golden Gate Technology (www.ggtcorp. com), global routing. Users then perform final routing, finishing, and BIST (built-in self-test) with eASIC tools. They can use any vendor's tool to perform ATPG (automatic-test-pattern-generation) testing. With the second flow, users feed a Verilog or VHDL netlist into an eAS-IC\Flextronics-only version of Magma's (www.magma-da. com) Blast SA, which incorporates the Aplus physicalsynthesis tool. The tool performs synthesis and placement and then feeds into eASIC's router, finishing tools, and BIST. As with the other flow, users can perform ATPG with any vendor's tool.

The companies currently fabricate the FlexASIC devices on STMicroelectronics' (www. st.com) 130-nm process. The companies claim that customers incur no NRE charges;

eASIC and Flextronics accommodate low-volume orders because they can implement a number of customers' designs, even if targeting a different part number of the eASIC family, on a single wafer. Vasishta says that companies have ironed out the lithography and design-for-manufacturing issues. A debugging technology is available, but customers can receive sample silicon as early as two weeks after tape-out so they can test their designs in their systems in real time. Package support for the family ranges from 100-pin TQFPs to 896-pin FBGA packages; eASIC is currently receiving tape-outs from beta customers and expects prototyping silicon by May and production silicon by July.

- —by Michael Santarini

- ▶eASIC, www.easic.com.

- ► Flextronics, www.flextron ics.com.

## **Even jacks are getting smarter**

THOUGH NOT THE FIRST jacks in audio's history with an auxiliary function, a new series from FCI USA brings the concept to the 38.5-mm-high BTX (Balanced Technology Extended) form factor, as well as to the 38.5-mm-tall jacks for the ATX (Advanced Technology Extended) form factor. The company's Smart Audio Jack series of triple-

stack connectors features an isolated switch so that associated circuitry can detect connector presence and also sense when a microphone, an audio input, or a speaker is plugged into the port. (Some designs use an electronic-circuit technique to make the same determination, but that approach can become complex because the jack must sense a completed—but highly variable and

uncontrolled—signal path.)

The color-coded jacks, targeting 192-kbps, high-definition audio designs, have initial 50-m $\Omega$  contact resistance and are rated for 1A current and 1000 insertion cycles. Price is 32 cents to 68 cents (1000), depending on configuration.—by Bill Schweber

▶FCI USA, www.fciconnect.com.

**20** EDN | APRIL 28, 2005 www.edn.com

## Accelerated. Samsung DDR2 memory helps reinvent the notebook.

Today's must-have notebook PCs feature supercharged performance, great battery life, sleek designs and dual-channel DDR2 memory. Get it from the DDR2 leader, Samsung, with the broadest selection of fully validated DDR2 SODIMMs. Available at speeds up to 533Mbps and densities from 256MB to 1GB. To find out more, visit the DDR2 microsite at www.samsungusa.com/semi/ddr2

Memory

Samsung, it's the performance inside.)

SAMSUNG

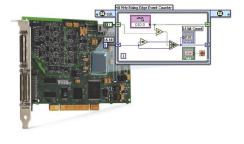

## FPGA development kit targets designs that "race"

Mercury Computer Systems has rolled out a development kit supporting the company's FPGA computing systems that employ its high-speed Race++ switch fabric. The FDK (FPGA Compute Node Developer's Kit) 2.0 platform, which includes software, IP (intellectual property),

and design consultation, offers the interconnect, communications, command and control, memory, and I/O functions for flexibility and quick deployment, according to the company.

The kit supports the company's IP cores for the ROC (Race-on-chip) high-bandwidth interconnect, a patentpending technology that extends the fabric inside the FPGA to access other IP cores, such as high-speed DRAM, SRAM, sensor-I/O, and system-level fabric interfaces, according to the company. The kit supports the PCI-based VantageRT FCN (FPGA-based compute node) and VME-based MCJ6 FCN

systems. Both of those products feature multimilliongate Xilinx (www.xilinx.com) FPGAs connected to Race++, which is Mercury's implementation of the industry-standard Raceway Interlink high-performance interconnect fabric.

Rich Jaenicke, Mercury's director of product management, says that FDK 2.0 helps users load bit streams into their FPGA and IP, providing an FPGA interface to components such as memories, switch fabric, and I/O. "Users have data streaming from a sensor into an I/O interface and are computing and storing data in memory and sending results over the switch fabric," Jaenicke says. "We are

providing infrastructure interfaces, which are helpful for our customers, because this approach allows them to focus on algorithms and not have to spend time on infrastructure." Engineers will also find the kit beneficial because it includes a dual DMA master/slave switch-fabric endpoint. "Switch fabrics are all the rage now, and this IP says that we have the switch fabric and all the protocol layers directly on the chip," Jaenicke says. FDK 2.0 is available now and costs \$23,000 for the first development seat, which includes 20 hours of development support.

—by Jeff Berman ►Mercury Computer Systems, www.mc.com.

## Single-chip FM tuner enables embedded broadcast receiver

What would EH Armstrong say? The FM (and superheterodyne) pioneer never envisioned an all-CMOS, single-IC FM tuner, such as the Si470x series from Silicon Laboratories. This highly integrated,  $4\times4$ -mm digital component needs just a bypass capacitor and takes less than 20 mm² of board space overall, far less than the typical approach, which requires a  $6\times6$ - mm IC, more than 30 support components, and  $150~\rm mm^2$  of space.

The single-chip tuner, the vendor asserts, is the industry's first all-CMOS device. It simplifies embedding a conventional broadcast FM receiver, spanning 76 to 108 MHz, into a cell phone or an MP3 player, for example, and thus it

is "easy and cost-effective to add FM radio as a standard feature to virtually any application," according to Ed Healy, vice president at Silicon Labs. And, even if you think broadcast radio is dead, many consumers do not; it is increasingly a feature on portable wireless devices.

The Si4700 version needs no alignment. It includes the required filtering, AGC (automatic gain control), a frequency synthesizer with a VCO (voltage-controlled oscillator), a low-dropout amplifier for direct battery connec-

tion, and audio-processing functions. The Si4701 adds an integrated preprocessor for the European RDS (Radio Data System) and the US RBDS (Radio Broadcast Data System) formats at a 57-kHz offset, which adds station ID and song name along with the music and allows alternate-channel (frequency) information, which European radio provides, in which a single broadcaster uses multiple frequencies.

The Si4700 sells for \$3 (10,000), and the Si4701 sells for \$3.50. The companion evaluation board costs \$150.

—by Bill Schweber

▶Silicon Laboratories Inc, www.silabs.com.

The all-digital, CMOS Si470x FM tuner does it all and in a  $4\times4$ -mm package, allowing designers to easily incorporate broadcast tuning into wireless handheld products.

► Checks accounted for 45% of all payments that were not made with cash in 2003, down from 57% in 2000, and 32% of US households used the Internet to pay bills in some fashion in 2004, according to TowerGroup.

22 EDN | APRIL 28, 2005 www.edn.com

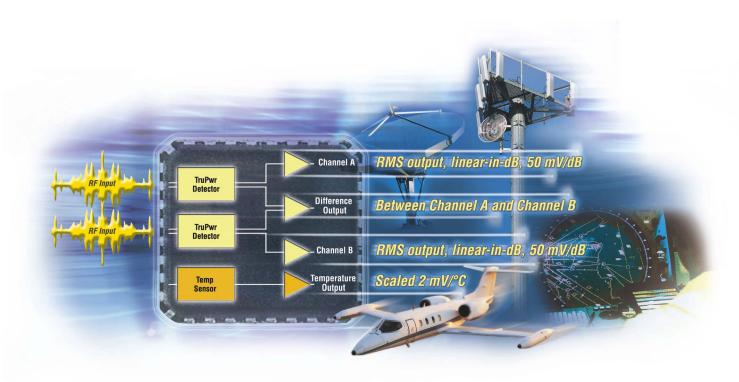

# Two complex RF signals. Three rms values. One IC.

#### AD8364 TruPwr™ Detector

- RMS power measurement from low frequency to 2.7 GHz

- Simultaneous dual-channel with difference output ports

- Integrated on-chip temperature sensor output

- Wide dynamic range: 60 dB @ 2.2 GHz

- Precision temperature-stable linear-in-dB rms outputs:  $\pm 0.5 \ dB$

- Operation: single 5 V supply, -40°C to +85°C

- Price: \$7.85 in 1k quantities

The AD8364 features a small footprint, 5 mm  $\times$  5 mm LFCSP package and provides lower cost and design-time advantages compared to logarithmic and discrete alternatives.

#### Introducing the industry's first dual-channel rms detector.

Accurately measuring complex, high order modulation signals, such as CDMA or OFDM, has long been one of the most difficult challenges RF designers face. With our introduction of the AD8364 TruPwr detector, designers will be able to precisely measure two rms values as dc outputs, along with a difference output between the two inputs and monitor temperature, in one IC. The AD8364 has the ability to measure signals with up to 60 dB of dynamic range and is independent of input frequencies up to 2.7 GHz, enabling the control of gain or loss within a transceiver. Or, with both inputs at the same frequency, the AD8364 can monitor a power amplifier's gain or VSWR. For more information, or to view the data sheet, please visit our website.

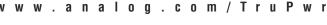

## Crosstalk in differential vias with grounds

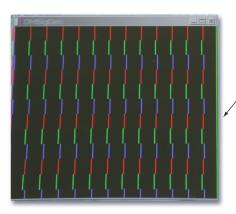

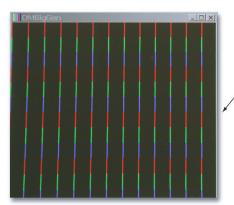

pable-module) committee, working on standards for 10-Gbps interconnections, published some terrific guidelines for high-speed differential vias (**Reference 1**). The guidelines propose surrounding your differential pair

with an oval clearance and pinning the reference planes together at either end of the clearance hole with ground vias (**Figure 1**).

The guidelines assume that no long dangling via stubs connect to your signal path, meaning that either (a) your signal goes all the way from the top layer to the bottom, or (b) in a less-than-fulllength transition, you have cut off the dangling ends of the via beyond the point at which signal current actually flows.

In boards as thick as 100 mils and with rise times on the order of 100

psec, the recommended structure produces a good,  $100\Omega$  transition between layers.

If you want to use this design in a dense architecture, you need to know about the crosstalk between these structures. To make the math easy, I will assume your layout provides a uniform grid of possible via locations, with a grid spacing of 0.8 mm and hole diameters of 0.3 mm. Index the grid by rows and columns.

Place one installment of the layout from Figure 1 with the topmost via at position Row 0, Column 0. The crosstalk voltages (millivolts) into this spot from other possible via locations appear in Table 1. For example, placing an aggressor pair one position to the right (one column over), the crosstalk from Table 1 in position Row 0, Column 1, reads 42 mV. I did these quasistatic calculations using MathCad.

Because the layout in Figure 1 is four positions long, if you stay in the same column, the closest you can place the next structure (shifting straight down) is four units. The shaded areas in the **table** designate impossible positions.

This table assumes a 2V p-p differential signal (that is, 1V p-p on each wire), driving  $100\Omega$  differential traces with 100-psec rise and fall times. The important aspect of this specification is the total change in current per unit time (dI/dt). Crosstalk in millivolts scales in proportion to dI/dt. If you have a lower voltage, a slower rise time, or a larger trace impedance, then scale down the numbers in Table 1 according to the extent of that difference in your architecture. As the table shows, crosstalk quickly plummets to small values as you separate aggressor from victim. Enforcing white space between signals is the surest way to guarantee low crosstalk.

What happens if you omit the ground vias? In that case, signals pass through the via in much the same way, but the crosstalk floats generally higher. More important, crosstalk falls off less rapidly with distance (**Table 2**). Ground vias help contain the electromagnetic fields emanating from each differential structure, arresting the spread of crosstalk.

#### REFERENCE

1. 10-Gigabit small-form-factor pluggable module, Revision 2.0, XFP multisource agreement.

Howard Johnson, PhD, author of High-Speed Digital Design and High-Speed Signal Propagation, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. howie03@sigcon.com.

## Talk to us

Post comments via TalkBack at the online version of this column at www.edn.com.

dards help with proper performance.

## TABLE 1—CROSSTALK IN MILLIVOLTS WITH GROUND VIAS

| Row/Column | 0 | 1  | 2 | 3 | 4 | 5 |

|------------|---|----|---|---|---|---|

| 0          | 0 | 42 | 5 | 1 | 0 | 0 |

| 1          | 0 | 23 | 1 | 0 | 0 | 0 |

| 2          | 0 | 3  | 2 | 0 | 0 | 0 |

| 3          | 0 | 3  | 0 | 0 | 0 | 0 |

| 4          | 1 | 0  | 0 | 0 | 0 | 0 |

| 5          | 0 | 0  | 0 | 0 | 0 | 0 |

## TABLE 2—CROSSTALK IN MILLIVOLTS WITH GROUND VIAS REMOVED

| Row/Column | 0  | 1  | 2  | 3  | 4 | 5 |

|------------|----|----|----|----|---|---|

| 0          | 0  | 85 | 27 | 13 | 7 | 5 |

| 1          | 0  | 14 | 15 | 10 | 6 | 4 |

| 2          | 35 | 14 | 1  | 4  | 4 | 3 |

| 3          | 14 | 10 | 3  | 0  | 1 | 2 |

| 4          | 8  | 6  | 4  | 1  | 0 | 1 |

| 5          | 5  | 4  | 3  | 2  | 1 | 0 |

24 EDN | APRIL 28, 2005 www.edn.com

## UNLEASH BROADBAND WITH FUJITSU'S WIMAX 802.16-2004 SoC.

With a MAC-to-PHY implementation based on the IEEE 802.16-2004 broadband wireless access standard, the Fujitsu WiMAX SoC, MB87M3400, offers a cost-effective solution for both subscriber station and base station applications. This highly integrated SoC implements MAC, PHY, radio control and all the necessary analog circuits for the appropriate 2 to 11GHz licensed or license-exempt bands. The Fujitsu WiMAX SoC fully complies with the IEEE 802.16-2004 standard using an OFDM PHY.

#### **ADVANCED FEATURES**

- 256 OFDM PHY with 64QAM, 16QAM, QPSK and BPSK modulation

- · Uplink subchannelization

- Flexible baseband interface with integrated high-performance ADC and DAC

- Security implementation using DES, CCM encryption/decryption

- Rich set of integrated peripheral and RF control

For more information, call (800) 866-8608 or visit http://us.fujitsu.com/micro/wimax

## Perception problem dogs engineering

has never been more difficult. From an attractiveness standpoint, engineering enjoyed brief life during Internet's early years, but has since returned to the more conservative realm that encourages only math and science

geeks. Since 1990, the number of bachelor's degrees in engineering has dropped 8%. More disturbing is a 20% decline in math degrees (Link 1). The reason for these declines is twofold, according to Geoffrey Orsak, School of Engineering dean at SMU (Southern Methodist University): One is that high-school students often shun science and math; most avoid taking them in college if they can. The other problem is image, and we can do something to improve it, contends Orsak, who is the antithesis of the engineering stereotype that, fairly or unfairly, has long tarnished the profession's image.

"Most believe it's one of the toughest majors, and so we are competing over a very small group of kids. But clearly engineering has an image problem even more than the perception that it's a challenging discipline," he says. That salaries for new engineers are among the highest compared with other professions doesn't seem to matter. "People see it as a bridge career from lower working class to a middle-class career. Once you reach that level, you want to go beyond it into law, medicine, and business leadership," he says.

That idea surprises me. I always admired people with a strong aptitude for math and science, probably because the two were not my strong suits. My civil-engineer uncle built interstates for 39 years, and I admire him. As a 19-year-old, his formidable math skills and intestinal fortitude landed him in the navigator's seat of a B-24 during World War II

and in an Rensselaer Polytechnic Institute classroom after that on the GI Bill. My 17-year-old son just aced the SAT II test in math. What does he want to be? A lawyer.

The decline in US engineers has become more noticeable because developing economies in countries such as China are cranking out new ones at four to six times the rate in the United States. And strong Jack Welch is a chemical engineer. Jimmy Carter is a nuclear engineer. Yasir Arafat was a civil engineer (Link 2). "If a doctor develops a new surgical technique, we celebrate it. We don't do that in engineering. I could name 10 famous doctors, but I could not name 10 famous engineers," says Orsak. That's why SMU has partnered with Texas Instruments to develop the Infinity Program, which attempts to dispel the myths and stereotypes that plague engineering in high-school classrooms (Link 3). The program trains high-school math and science teachers to make engineering fun, cool, interesting, and accessible to broader range of prospects.

That the numbers of new engineers hasn't changed for decades in-

## WE CAN'T LOWER THE ACADEMIC BAR, SO WE HAVE TO INSTEAD SPRUCE UP ENGINEERING'S IMAGE.

growth in retirements as the engineering workforce ages will compound the problem. More than half of the engineers in the United States are older than 40, says the NSB report.

What can the United States do about this problem? Clearly, we can't lower the academic bar, so we have to instead spruce up engineering's image. "We have to celebrate our people. As long as we continue to view engineering as about widgets and not about people, we will have a perception problem," says Orsak. Engineering needs highly visible heroes, just as the business world has Michael Dell and Bill Gates. Such heroes motivate students to take a similar path. But engineering has plenty of Dells and Gates. The problem is that they generally don't seek recognition, except, perhaps, from peers. There are plenty of successful engineers, but they either labored in obscurity or took another path. Former General Electric Chief Executive Officer dicates the magnitude of the problem. And what we do now to convince more high-school students to choose engineering won't pay off in national competitiveness for a decade. Currently, approximately 65,000 engineers a year graduate from US schools, says Orsak. "It's never been over 100,000 and never below 50,000 for the past 30 years. But many more kids go to college today, and we thought a rising tide would lift all boats."

Do you have an engineering hero? Write me at john.dodge@ reedbusiness.com.

## Links

- 1. "Science and Engineering Indicators 2004," National Science Board, www.nsf.gov/sbe/srs/seind 04/c0/c0s1.htm.

- 2. *The Encyclopedia Britannica*, www.britannica.com/nobel/micro/30\_1.html.

- 3. www.infinity-project.org/join/join\_video.html.

26 EDN | APRIL 28, 2005 www.edn.com

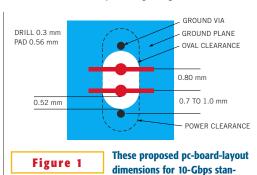

# Lowest Crosstalk 10.7Gbps Single & Dual 2.5V 2x2 CML Crosspoint Switches

Ultra-low 0.7ps<sub>RMS</sub> Crosstalk-Induced Jitter, <10ps<sub>P-P</sub> Total Jitter

Micrel's new SY58023U and SY58024U are ultra-fast single and dual 2x2 crosspoint switches, optimized for Layer 1 data applications that require the lowest jitter and highest crosstalk isolation between channels. They can process clock signals as fast as 6GHz or data patterns up to 10.7Gbps.

Extremely flexible, they can be used as a 2:1 multiplexer, 2x2 crosspoint switch, dual buffer or a dual any-differential-input-to-CML translator. They directly interface to any differential signal (DC- or AC-coupled) without any level shifting or termination resistor network in the signal path. The CML outputs feature 400mV swing into  $50\Omega$  loads, and an extremely fast rise/fall time of less than 60ps guaranteed over temperature and voltage.

For more information, please contact your local Micrel sales representative or visit us at: http://www.micrel.com/ad/switches.

## The Good Stuff:

- ◆ Guaranteed data throughput: DC-to->10.7Gbps

- Guaranteed ultra-low jitter:

- <1ps<sub>RMS</sub> random jitter

- <10ps<sub>PK-PK</sub> deterministic jitter & total jitter

- <0.7ps<sub>RMS</sub> crosstalk induced jitter

- lacktriangle CML outputs reduce reflections with 50 $\Omega$  internal source-terminated outputs

- lacktriangle Unique patent-pending input termination and  $V_T$  pin accepts both DC- and AC-coupled differential inputs: LVPECL, LVDS, CML

- Unique patent-pending input isolation design minimizes channel-to-channel crosstalk

## **Choose Your High-Speed 2x2 or 4x4 Crosspoint Switch**

|      | Part No. | Channels   | Max. Data<br>Throughput | Guaranteed Pk-Pk<br>Total Jitter <sup>1</sup> | Internal<br>I/O Termination | Package &<br>Footprint | Price <sup>2</sup> |

|------|----------|------------|-------------------------|-----------------------------------------------|-----------------------------|------------------------|--------------------|

|      | SY55858U | Dual 2x2   | 3.0Gbps                 | <20ps                                         | ✓                           | 32-pin TQFP 9mm x 9mm  | 7.28               |

|      | SY55859L | Dual 2x2   | 2.7Gbps                 | N/A                                           | MAX3840 Alt. Src.           | 32-pin MLF™ 5mm x 5mm  | 7.95               |

| NEW! | SY58023U | Single 2x2 | >10.7Gbps               | <10ps                                         | ✓                           | 16-pin MLF™ 3mm x 3mm  | 7.95               |

| NEW! | SY58024U | Dual 2x2   | >10.7Gbps               | <10ps                                         | ✓                           | 32-pin MLF™ 5mm x 5mm  | 9.80               |

| NEW! | SY58040U | 4x4        | >5Gbps                  | <10ps                                         | /                           | 44-pin MLF™ 7mm x 7mm  | 9.99               |

| NEW! | SY89540U | 4x4        | >3.2Gbps                | <10ps                                         | Input Termination           | 44-pin MLF™ 7mm x 7mm  | 6.95               |

- 1. TJ defined: with an ideal clock source of frequency sfmax, no more than one output edge in 1012 output edges will deviate by more than the specified jitter value.

- 2. 1,000 piece suggested resale, FOB USA

Literature: 1 (800) 401-9572 Factory: 1 (408) 944-0800 Stocking Distributors: Arrow 1 (800) 777-2776

> Future 1 (800) 388-8731 Newark 1 (800) 463-9275 Nu Horizons 1 (888) 747-6846

## **Intersil Switching Regulators**

Intersil High Performance Analog

# The Smart Dogs Just Know How To Keep Their Cool

Intersil's new high current Integrated FET Regulators have some new tricks to teach the old dogs, including the industry's only true Thermal Protection with auto shut down at 135°C.

Intersil's EL7554 and EL7566 DC-DC buck regulators with internal CMOS power FETs operate from 3V-to-6V input voltage and are capable of up to 96% efficiency. But what's really cool about these devices is ground breaking features like built-in Thermal Protection and Voltage Margining for actual in-circuit performance validation.

## HTSSOP THERMAL RESISTANCE vs PCB AREA (NO AIR FLOW) 50 The first line of defense against heat is a thermally-efficient HTSOP-28 45 package, which utilizes an exposed thermal pad 40 underneath the IC to spread heat through the PCB. 30 The V<sub>TJ</sub> pin is a formula-based, accurate indicator of the internal silicon junction temperature PCB Area (in2) If all else fails and the temperature sensor indicates a junction temperature above 135°C, the PWM Regulator ± 0.047µF will shut down. .7μH \(\bar{1}\)100μF 150µF

### **Key Features:**

- 4A (EL7554) and 6A (EL7566) continuous output current

- Up to 96% efficiency

- Built-in 5% voltage margining

- 3V-to-6V input voltage

- 0.58 in<sup>2</sup> (EL7554) and 0.72 in<sup>2</sup> (EL7566) footprint with components on one side of PCB

- Adjustable switching frequency to 1MHz

For more information and samples, go to www.intersil.com/edn

Easy-to-use simulation tool also available. Modify switching frequency, voltage ripple, ambient termperature and view schematics waveforms, efficiency graphs and complete BOM with Gerber layout.

Enter 14 at www.edn.com/info

VDO

THE GROWTH OF ELECTRONIC SUB-SYSTEMS IN VEHICLES DEMANDS NETWORKS FROM THE MISSION-CRITICAL TO THE MUNDANE. THE LOCAL-INTERCONNECT-NETWORK PROTOCOL TACKLES THE TASK.

ITH PREDICTIONS suggesting a global annual-compoundgrowth rate of some 8.3% over the next five years, the automotive sector continues to be our industry's fastest growing market. It's sobering to consider that, barely 20 years ago, the sole electronics content within most vehicles was a radio. Then came the electronic ignitions, engine-management units, and antilock-braking systems that are standard in today's entry-level cars. Now, of course, vehicles include previously unheard-of luxuries, and top-of-the range vehicles adopt sophisticated electronics, such as intelligent cruise controls that automatically maintain a safe distance from the vehicle ahead. Estimates suggest that the electronics content of an average car now accounts for no less than 22% of its manufacturing cost, creating markets for the embedded controllers, power devices, and communications technologies that link its ECUs (electronic-control units).

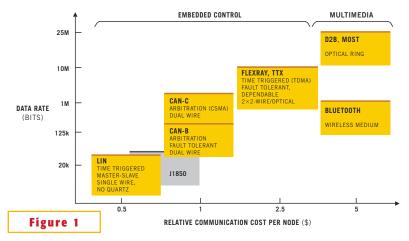

Recognizing the need for a robust in-vehicle network to manage distributed intelligence and reduce wiring-harness dimensions, Bosch in 1986 designed a CAN (controller-area network). Today, CANs dominate in-vehicle networking and have also made the transition to multiple industrial uses. In the meantime, other networking systems have appeared to tackle emerging automotive applications. These technologies include D2B (domestic-digital-databus), FlexRay, and MOST (media-oriented system transport), all of which employ fiber media for speed and EMC resistance. TT-CAN (time-triggered extensions to CAN) improve the protocol's determinism, as well as the TTP (time-triggered-protocol) series that competes with FlexRay for safety-critical use (**Reference 1**). Because these systems serve high-

end applications and are relatively expensive, designers require a low-cost alternative to serve mundane tasks, such as to control body functions from seats to sunroofs. As a result, car makers increasingly embrace LINs (local-interconnect networks), which position themselves at the lowest level in the automotive-networking hierarchy (**Figure 1**).

The first LIN specification appeared in 1999. Among the founding members of the LIN Consortium, its design authority, are car makers BMW, DaimlerChrysler, Volkswagen Audi Group, and Volvo Cars, together with hardware and networking expertise from Freescale Semiconductor and Volcano Automotive Group. Design influences include the Vlite bus that several car makers use, as well as lessons accruing from many years of CAN evolution and development. Several amendments culminated in LIN Version 1.3 in November 2002, which many observers regard as the first stable release. Further work resulted in a major revision that appears as the current Version 2.0 of September 2003, which the LIN Consortium recommends for all new development.

Meanwhile, in North America, the Society of Automotive Engineers issued its J2602 recommended practice, "LIN Network for Vehicle Applications," with key car-maker representation coming from Ford and General Motors. The main differences between LIN 2.0 and J2602 include limiting the transmission rate to 10.4 kbps and modifying some protocol details, such as error handling. Some observers feel that J2602's objectives include limiting feature creep, thus making it easier to meet LIN's overriding low-cost target using, for example, state-machine logic rather than microcontroller-based intelligence.

www.edn.com April 28, 2005 | Edn 29

# Master your next design challenge!

© National Semiconductor Corporation, 2004. National Semiconductor,

are registered trademarks of National Semiconductor Corporation. All rights reserved.

Make your design a reality with our easy, interactive design environment.

View **over 85 applications** containing:

- System overview

- · Color-coded block diagram

- List of recommended parts, parameters and pricing

Perform design simulations in our WEBENCH® virtual lab and receive your customized prototype kit within 24 hours!

Use National's comprehensive suite of *free* design tools to help you perfect your designs quickly.

Find your next solution at: solutions.national.com

## design**feature** Local-interconnect networks

The LIN Consortium's objectives for its new system don't stop with low cost, although, because LIN is markedly cheaper than CAN or the J1850 domestic-US standard, cost is the prime driver. In fact, with original predictions for LIN lying at around \$1/node, it is currently proving hard to meet this cost target. But, in its primary role as a sub-bus, LIN's design ensures that it functions as a logical and scalable extension of CAN and J1850. It provides acceptable reliability for nonsafety-critical tasks, with less-than-100msec response times and predictable worst-case timing characteristics. Learning from previous bus evolutions, the developers were also careful to consider tool-chain-support issues. Such considerations have become crucially important as the car makers forge seamless co-development links with their system suppliers.

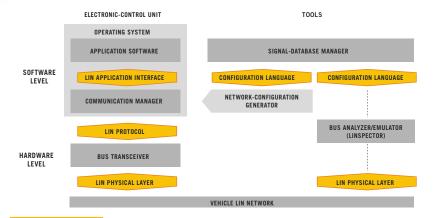

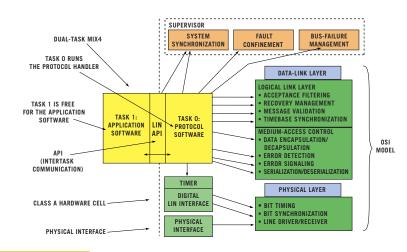

Naturally, the specification must ensure hardware and software interoperability among multiple vendors, as well as minimizing peripheral but critical issues, such as EMC. From the outset, LIN's specifications accordingly subdivide into three main parts that describe the transmission medium and its communication protocols, a configuration language, and APIs (application-programming interfaces) (Figure 2). Representing the lowest two levels of the ISO/IEC 7498-1:1994 opensystems-interconnect model, the protocol specification tackles the physical-layer and data-link-layer mechanisms. At the highest level, an API abstracts the user's code from lower level network mechanics; in between, a signal interaction and diagnostic layer decouples the application from the network. To furnish a standard interface between LIN nodes from mul-

#### AT A GLANCE

Description > LIN (local-interconnect network) challenges CAN (controller-area network) for lowest cost in noncritical applications.

► Version 2.0 introduces new plugand-play capability but costs memory.

▶ Vendors offer a dazzling palette of hardware support.

▶ Future growth prospects include consumer goods and industrial use.

tiple suppliers, the LIN configurationlanguage description defines the format of the files that configure the network. These configuration files also provide hooks into development tools. In a further and major forward step, 2.0 introduces the LIN-node-capability language, easing integration via a plug-and-play concept (see **sidebar** "LIN 2.0 goes plug and play" on the Web version of this article at www.edn.com).

#### ONE-WIRE MASTER/SLAVE ARCHITECTURE

To minimize cost and wiring weight, LIN uses a single-conductor, wire-OR bus that takes advantage of a car's body shell to serve as a common ground. Each LIN subnet comprises one master and at least one slave node to a maximum of 16 devices per bus. Nodes can participate on more than one LIN bus, and masters may also operate as bridges into other network environments, typically CANs. Maximum transmission speed and reach are 20 kbps and 40m, respectively, using UART/SCI communications. This technology makes LIN implementations pos-

LIN tackles the lowest level of the in-vehicle-networking hierarchy.

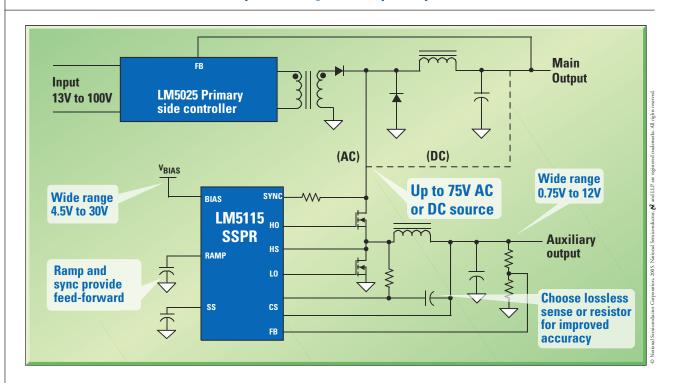

## Secondary-side post regulator (SSPR) doubles as high-voltage DC-DC controller

## Feature-rich LM5115 controller simplifies design of multiple output DC-DC converters

#### LM5115 Features

- Provides multiple outputs from main DC-DC or AC-DC converter

- Operates directly from secondary-side phase signal or DC input

- Leading-edge modulation for SSPR from current-mode primary controller

- Up to 1 MHz switching frequency reduces component footprint and profile

- Integrated gate drivers with 2.5A peak output current

- Available in TSSOP-16 and tiny LLP-16 packaging

Ideal for use as a secondary-side post regulator in the design of multiple output AC-DC or DC-DC power supplies or as a DC-DC controller for use in point-of-load (POL) regulators

Shown actual size

TSSOP-16 4.4 x 5.0 x 0.9 mm

For FREE samples, evaluation boards, datasheets, and online design tools, visit us today at

power.national.com

Or call 1-800-272-9959

## design**feature** Local-interconnect networks

Figure 2

LIN defines the physical-layer, protocol-handler, and application-programming interfaces with support from a configuration language.

sible with drivers ranging from simple state-machine logic to "bit-bashing" an I/O pin in software to using serial peripherals. Such low speeds also constrain interference generation and ease timing issues, assisted by a master-driven self-synchronization facility that allows slave nodes to dispense with crystal or resonator timers.

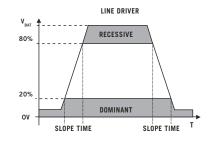

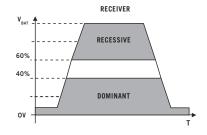

Physical-layer exchanges employ an enhancement to the ISO-9141 standard that dominates European and Japanese vehicle-diagnostic systems. LIN-compatible line drivers limit slew rate to around 2V/µsec to avoid creating interference due to fast edges. Such a line driver asserts the "dominant" logic-zero state by driving the bus line to within 20% of system ground; a "recessive" logic one requires driving the line to within 20% of battery voltage. To allow for effects such as ground shift, receivers allow more tolerance, acknowledging levels within 40% of the respective rails (Figure 3). The master terminates the bus with a 1-k $\Omega$ resistor to battery voltage, and each slave defaults its I/O line high with a 30-k $\Omega$ pullup resistor. A diode in series with the termination resistor prevents devices on the bus from backfeeding into the battery-voltage rail if the supply fails. Masters and slaves also each present around 220 pF to the line up to a maximum of 10 nF per bus, which results in a system time constant of 1 to 5 µsec. In a region in which AM radios still proliferate, SAE-J2602's 10.4-kbps limitation further eases compatibility issues for the North American market.

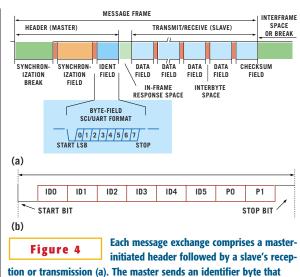

Unlike CAN, LIN's master/slave architecture avoids data-traffic collisions and the need for arbitration logic by having

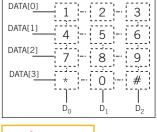

the master supervise message transmissions, thus ensuring that only one message transmits at any time. A frame consisting of the master's header, a pause, and a slave's response encapsulates each message exchange (Figure 4a). Start and stop bits surround each byte, resulting in a 10bit transmission per byte. There are several frame types, starting with diagnostic frames that carry diagnostic or initialization information. By contrast, "unconditional frames" always carry signals of as many as eight bytes. These are the frame types typify applications. "Sporadic" frames also always carry signals, but slaves respond only if new data is available, otherwise leaving the data field blank-an attempt to add some dynamic behavior into the system's schedule without compromising its determinism. Polling infrequently responding nodes generates bus traffic. To improve system responsiveness by reducing the bus traffic, the protocol includes an event-triggered frame. This frame accommodates as many as seven data bytes, because the first field carries an identifier that associates the frame with its task. Again, slaves respond only if they have new data. The protocol also provides for user-defined frames and reserves another type for future use.

To initiate a data transfer following an interframe space or bus-idle condition, the master transmits a header comprising a synchronization-break period, a single-byte-synchronization field, and an identifier byte. The identifier byte carries six bits of information and two parity bits, allowing 64 message identifiers (Figure 4b). In normal operation, there is no addressing as such; rather like CAN, the identifier byte uniquely defines the purpose of the frame. Identifier decimal values of zero to 59 carry signals; 60 and 61 are master-request and slave-response diagnostic frames, respectively; user-defined frames have a header value of 62; and 63 is reserved. Each slave waits for the synchronization break and locks onto the synchronization byte before scanning the bus message. One or more slaves then receives data, or a single slave transmits response data. The data field accommodates eight bytes; the data field's association with its identifier byte predefines the field's length. A single-byte check field terminates the transmission, providing an error-detection facility. The master is responsible for all error handling, which is in turn the application programmer's responsibility; LIN 2.0 has no defined error-handling mechanism.

Because it's imperative to preserve battery power when the vehicle is inoperative, slaves automatically enter sleep mode if the bus is idle for more than four seconds. The master can also force slaves into sleep mode by sending the diagnostic master-request frame with the first data byte set to zero. The master subsequently monitors the bus when it is idle, looking for wake-up signals from slaves that require service. Any bus node can request wake-up by asserting the dominant state for 250 µsec to 5 msec, which makes 5 msec the dominant state's longest valid

Receivers tolerate levels of as much as 40% of the supply rails to account for effects such as ground shifts.

32 EDN | APRIL 28, 2005 www.edn.com

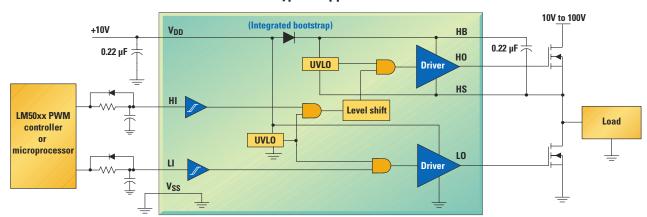

# 100V Half-bridge power MOSFET drivers offer industry's highest peak gate drive current

New LM510x drive both the high and low-side N-Channel MOSFETs in synchronous buck or half-bridge configurations

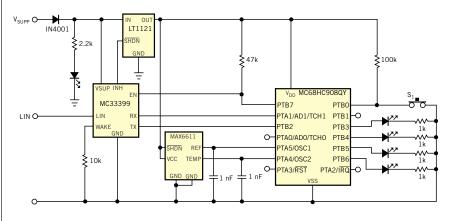

## LM510x Typical application circuit

- Flexible configurations: interleaved forward, cascaded push-pull, half-bridge or full-bridge

- User-programmable turn-on edge delay feature (LM5105)

- New high-voltage bootstrap diode

- Best-in-class speed and efficiency in high-frequency switching regulator applications

- Negative load voltage transient capability down to -5V (LM5105/7)

- Available in SOIC and tiny, thermally enhanced LLP packaging

|     | Peak Gate Current | Product ID  | Input Threshold | Packaging    | Comments                                           |

|-----|-------------------|-------------|-----------------|--------------|----------------------------------------------------|

| NEV | 3.0A              | LM5100A/01A | CMOS / TTL      | LLP-10, SO-8 | Upgrade of HIP2100/01                              |

| NET | ▶ 1.8A            | LM5105      | TTL             | LLP-10       | Programmable dead-time, negative $V_{\text{LOAD}}$ |

| NEV | 1.4A              | LM5107      | TTL             | LLP-8, SO-8  | Upgrade of ISL6700, negative V <sub>LOAD</sub>     |

Ideal for half-bridge and full-bridge power DC-DC converters, cascading current-fed or voltage-fed DC-DC converters, high-voltage buck DC-DC converters, and solid-state motor and solenoid drivers

For FREE samples, datasheets, online design tools, and more, visit us today at

power.national.com

Or call 1-800-272-9959

run. Most transceivers incorporate a watchdog timer that disconnects nodes exceeding this maximum, because such behavior indicates an error condition that would otherwise monopolize the bus. Slaves must wake up and be ready to transmit data within 100 msec of the end of the wake-up signal. Crucially, because the message length, interframe-spacing parameters, and device-wake-up times are known, it's easy to calculate worstcase response times for any system. Masters typically use a static, round-robin scheduler, although adaptive schedulers provide greater flexibility to permit decision-based systems that similarly have guaranteed determinism.

An exception to the zero-collision rule occurs when the master polls for an eventtriggered frame and more than one slave responds within the same time slot. This situation might arise, for example, when the master polls all the doors within a central-locking application using an eventtriggered frame. The response would normally be blank, but if more than one door button is active at this instant, more than one slave responds. The master resolves the collision by requesting all of the unconditional frames of similar association and checks their event flags before again requesting the event-triggered frame. This sequence avoids the possibility of a slave's withdrawing from a collision without corrupting the data, which the master would not detect, and thus lose the slave's response. Because application software implements these sequences, the programmer must ensure that the bus has enough time to complete its operations without

compromising the system's schedule. At the scheduler level, it's not permissible to include unconditional frames that are associated with either a sporadic or an event-triggered frame within the same schedule table as the sporadic or the event-triggered frame.

### SIMPLICITY BELIES CHALLENGES

Although LIN is conceptually simple, device vendors still face significant challenges. The first difficulty is to fabricate bus transceivers that withstand automotive conditions, notably severe EMC-test compliance. Although LIN constrains interference generation through

baud- and slew-rate limiting, it's important that the system withstands severe levels of radiated and conducted emissions. Against a background of emissions and interference issues, car makers have developed a range of in-house tests for evaluating in-vehicle networks. These essentially consist of injecting RF interference into the bus and varying the signal's frequency, amplitude, and modulation depth until the system fails. Many common elements of these proprietary tests appear in the LIN-conformance test suite, which agencies such as the Communication and Systems Group at Fachhochschule University of Applied Sciences specialize in applying on behalf of its clients.

Scott Monroe, system architect at Texas Instruments' mixed-signal power and control group, explains that bulk-currentinjection tests are popular in the United States, whereas European car makers favor DPI (direct-power-injection): "With DPI, you increase the RF-power levels into a bus of, say, three or four transceivers, via an RC coupler until the system breaks. With bulk current injection, the bus runs through a coupling coil, and you again vary the interference levels, looking for the point where message transmissions fail." Monroe notes that the LIN specifications don't mention protection against reversebattery faults and negative-going transients, such as those that inductive loads create. These tests form part of the CISPR (International Special Committee on Radio Interface)-25 and ISO (International Organization for Standardization)-7637 transient-immunity standards for automotive ICs. With a ±40V bus fault and as much as 17-kV ESD protection, TI's TPIC1021 withstands these rigors and improves system reliability with features such as dominant-state time-out. Its I/O pins use a 5V-tolerant 3.3V structure for maximum logic compatibility. With thermal and bus-terminal protection from shorts to either supply rail, the chip doesn't disturb other bus communications in its inactive state. It responds to wake-up requests from the bus, from an enable pin that connects to the host microcontroller, or to a battery-voltage level-switch input. In sleep mode, quiescent current consumption falls from a maximum of around 2.5 mA to about 20 µA. The chip can also control an external voltage regulator, making it possible to power down a microcontroller or other LINprotocol logic.

Other vendors that offer LIN transceivers include AMI Semiconductor, Atmel, Freescale, Infineon, Melexis, Microchip, On Semiconductor, Philips, STMicroelectronics, Yamar, and ZMD. Like the TI part, many of these devices offer similar pinout and functions to Freescale's MC33399 and Philips' TJA-1020 market-leading transceivers. Philips has a useful application note that illuminates LIN-transceiver issues (Reference 2). There are, however, detail differences between the electrical specifications in various competitive products, such as in the fault-voltage tolerance that vendors quote. For example, Atmel's ATA6661 withstands bus voltages of as much as 60V for use in 42V PowerNet environments. There are also some subtle differ-

ences between apparently similar pinouts. For example, although most transceivers run directly from the vehicle's battery voltage, On Semiconductor's NCV7380/7382 requires a 5V supply on Pin 3, which is typically a battery-voltage-compatible wake-upsignal pin. The NCV7380 variant also dispenses with sleep-mode logic to minimize cost.

Gilles Guillaume of On Semiconductor's European marketing operation notes that the company offers designers extra flexibility, such as a voltage-regulator option to derive auxiliary power. In-

**34** EDN | APRIL 28, 2005 www.edn.com

uniquely defines the frame's purpose within a system (b).

## Intersil Video Products

Intersil High Performance Analog

## Video Performance Over CAT-5 Cable Driving You Crazy?

Intersil's EL9115, a triple analog delay line, compensates skew introduced by CAT-5 cable, enabling high-quality video through 1,000 feet of cheap twisted pair cable.